## **Escuela Politécnica Superior**

## Departamento de Tecnología Electrónica y de las Comunicaciones

## AN INNOVATIVE VISION SYSTEM FOR INDUSTRIAL APPLICATIONS

## PHD DISSERTATION Ricardo Ribalda Delgado

Madrid, October 2015

Supervised by Javier Garrido Salas

## PROCEEDING

The Dissertation Committee approves, and recommends for acceptance for the degree of Doctor of Philosophy, the Thesis by Ricardo Ribalda Delgado: AN INNOVATIVE VISION SYSTEM FOR INDUSTRIAL APPLICATIONS.

Dr. Jesús M. González Barahona Chairman Dr. Guillermo González de Rivera Peces Secretary

Dr. Brian Vinter

Dr. Bjarke Jørgensen

Dr. Gustavo Sutter Capristo

With the grade of:

Madrid, 20th. November 2015

## ABSTRACT

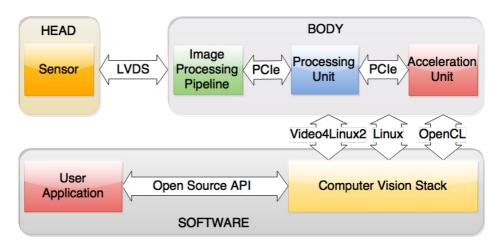

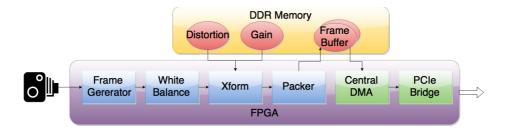

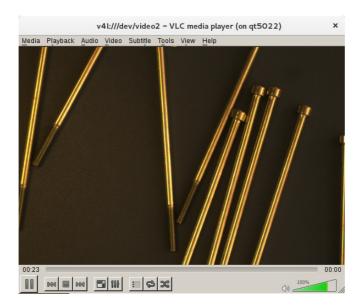

Despite the fact that computer vision systems place an important role in our society, its structure does not follow any standard. The implementation of computer vision application require high performance platforms, such as GPUs or FPGAs, and very specialized image sensors. Nowadays, each manufacturer and research lab develops their own vision platform independently without considering any inter-compatibility. This Thesis introduces a new computer vision platform that can be used in a wide spectrum of applications. The characteristics of the platform has been defined after the implementation of three different computer vision applications, based on: SOC, FPGA and GPU respectively. As a result, a new modular platform has been defined with the following interchangeably elements: Sensor, Image Processing Pipeline, Processing Unit, Acceleration unit and Computer Vision Stack. This thesis also presents an FPGA synthetizable algorithm for performing geometric transformations on the fly, with a latency under 90 horizontal lines. All the software elements of this platform have an Open Source licence; over the course of this thesis, more than 200 patches have been contributed and accepted into different Open Source projects like the Linux Kernel, Yocto Project and U-boot, among others, promoting the required ecosystem for the creation of a community around this novel system. The platform has been validated in an industrial product, Qtechnology QT5022, used on diverse industrial applications; demonstrating the great advantages of a generic computer vision system as a platform for reusing elements and comparing results objectively.

## RESUMEN

A pesar de que los sistemas de visión por computadora ocupan un puesto predominante en nuestra sociedad, su estructura no sigue ningún estándar. La implementación de aplicaciones de visión requiere de plataformas de alto rendimiento tales como GPUs o FPGAs y el uso de sensores de imagen con características muy distintas a las de la electrónica de consumo. En la actualidad, cada fabricante y equipo de investigación desarrollan sus plataformas de visión de forma independiente y sin ningún tipo de intercompatibilidad. En esta tesis se presenta una nueva plataforma de visión por computador utilizable en un amplio espectro de aplicaciones. Las características de dicha plataforma se han definido tras la implementación de tres aplicaciones de visión, basadas en: SOC, FPGA y GPU, respectivamente. Como resultado, se ha definido una plataforma modular con los siguientes componentes intercambiables: Sensor, procesador de imágenes "al vuelo", unidad de procesado principal, acelerador hardware y pila de software. Asimismo, se presenta un algoritmo para realizar transformaciones geométricas, sintetizable en FPGA y con una latencia de tan solo 90 líneas horizontales. Todos los elementos software de esta plataforma están desarrollados con licencias de Software Libre; durante el trascurso de esta tesis se han contribuido y aceptado más de 200 cambios a distintos proyectos de Software Libre, tales como: Linux, YoctoProject y U-boot, entre otros, promoviendo el ecosistema necesario para la creación de una comunidad alrededor de esta tesis.Tras la implementación de la plataforma en un producto comercial, Qtechnology QT5022, y su uso en varias aplicaciones industriales se ha demostrado que es posible el uso de una plataforma genérica de visión que permita reutilizar elementos y comparar resultados objetivamente.

A mis padres y hermana A Mariana

## ACKNOWLEDGEMENTS

During this (long) journey I have had the pleasure and the chance of being surrounded by an outstanding group of people.

The first person I want to thank is my supervisor, Javier Garrido. He has been undoubtedly the pillar that has supported all the pieces together and has lead them to this final composition. He has been a guide both in my academic and personal life. *Muchas gracias Javier, esta Tesis es tuya*.

The second person I want to thank is my friend and current boss, Kristian Madsen. He has given me freedom to work on my Thesis and trust to execute my ideas in his company. During the last five years I have learn the meaning of the word Engineer. *Tusind tak Kristian*.

Then I want to thank Tom Neubert and the rest of the team at Jüelich (George, Heinz, Tobias, Anne...): I have enjoyed every single day of my internship in your lab where I discover my passion, and now, my work: Embedded Design. *Vielen dank Tom!*

I also want to thank the Open Source community for their help and patience, I am particularly thankful to Hans Verkuil and the rest of linux-media.

It is a pleasure to mention the place that saw and valued my first steps as an engineer and which I remember always with happiness: HCTLAB and all the people there (past and present): Susana, Guillermo, Ángel, Pepe, Fernando, Alberto, Javier Tejedor, Victor, Daniel, Antonio, Nico....

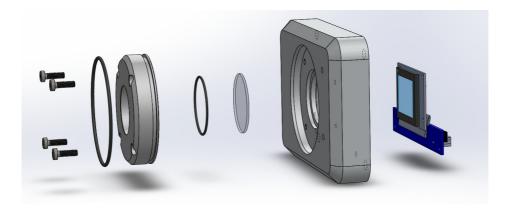

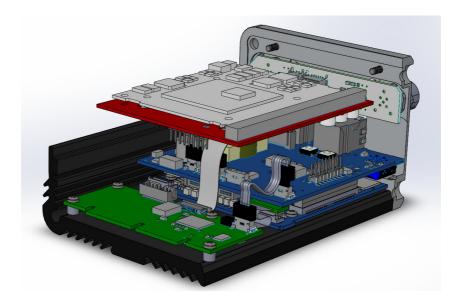

I do not forget the rest of Qtechnology, a lot of the work shown here has been done with their support: Alexandre Desnoyers is the author of most of the PCBs of the QT5022, and a walking encyclopedia for anything with a wire. Finn Nielsen has implemented most of the custom FPGA cores for the QT5022. Jean Claude Thibault has designed the rest of the PCBs and cores. Marianna Buschle has implemented the calibration tools of the device. Dimitrios Katsaros has worked on the test framework that validate the cameras. Thomas Clausen is the author of the 3D designs. Without their work, this Thesis would be nothing more than another prototype made with a commercial board that has no use outside the Academia.

Other friends have reviewed this text with infinite dedication. Juanjo, you have imprinted a very professional level in this text, thank you very much for all the time expend and I wish you all the best with your new child.

I should mention also two brave colleagues that have made the tough decision to leave Spain to continue with their careers: Bruno and Carmen, thanks for your help mates !

I want to publicly acknowledge my parents for their support during my entire life. *Muchas gracias papás, todo en esta vida os lo debo a vosotros. Nunca podré daros suficientes gracias por los sacrificios que habéis hecho por mi hermana y por mí.*

And of course my wife, for her infinite patience during these years, for being the travel partner of my life and for giving me support and love every single time that I needed it.

I have probably forgot to mention a lot of people, I'm sorry about that, as I said, this has been a very long journey and I am getting too old to even remember my own name :).

Finally, I want to thank you, yes you! whoever you are, for using your time reading this Thesis. I hope that you can enjoy reading it as much as I enjoyed writing it.

| i  | INTI                                             | RODUCTION AND STATE OF THE ART 1                 |  |  |  |  |  |

|----|--------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

| 1  | INTRODUCTION 3                                   |                                                  |  |  |  |  |  |

|    | 1.1                                              |                                                  |  |  |  |  |  |

|    | 1.2                                              | Design Goals 7                                   |  |  |  |  |  |

|    | 1.3                                              | History of the Project 8                         |  |  |  |  |  |

|    | 1.4                                              | Structure of the document 9                      |  |  |  |  |  |

| 2  | STATE OF THE ART 11                              |                                                  |  |  |  |  |  |

|    | 2.1 Definition 13                                |                                                  |  |  |  |  |  |

|    | 2.2                                              | Industrial Computer Vision 14                    |  |  |  |  |  |

|    | Computer Vision Stages 14                        |                                                  |  |  |  |  |  |

|    | 2.4 Computer Vision Computation Architectures 16 |                                                  |  |  |  |  |  |

|    |                                                  | 2.4.1 Digital Signal Processors 16               |  |  |  |  |  |

|    | 2.4.2 Field Programmable Gate Arrays 17          |                                                  |  |  |  |  |  |

|    |                                                  | 2.4.3 Cluster Computing 17                       |  |  |  |  |  |

|    |                                                  | 2.4.4 General Purpose Graphics Processor Unit 17 |  |  |  |  |  |

|    | 2.5                                              | Computer Vision Platforms 18                     |  |  |  |  |  |

| ii | CUS                                              | STOM COMPUTER VISION SYSTEMS 21                  |  |  |  |  |  |

| 3  | EMBEDDED SYSTEM ON CHIP COMPUTER VISION 23       |                                                  |  |  |  |  |  |

|    | 3.1 Introduction 25                              |                                                  |  |  |  |  |  |

|    |                                                  | 3.1.1 Classical Biometric Systems 25             |  |  |  |  |  |

|    |                                                  | 3.1.2 X.509 digital certificates 28              |  |  |  |  |  |

|    | 3.2 System-on-Token 29                           |                                                  |  |  |  |  |  |

|    |                                                  | 3.2.1 System on Token Architecture 29            |  |  |  |  |  |

|    |                                                  | 3.2.2 Transactions 31                            |  |  |  |  |  |

|    | 3.3 Implementation 32                            |                                                  |  |  |  |  |  |

|    |                                                  | 3.3.1 Device Selection 32                        |  |  |  |  |  |

|    |                                                  | 3.3.2 Biometric Module 33                        |  |  |  |  |  |

|    |                                                  | 3.3.3 Certificate Module 35                      |  |  |  |  |  |

|     | 3.4 Dataflow 35                                      |

|-----|------------------------------------------------------|

|     | 3.5 Conclusions 36                                   |

| 4   | FPGA COMPUTER VISION SYSTEM 37                       |

|     | 4.1 Introduction 39                                  |

|     | 4.2 FPGAs with embedded CPU cores 39                 |

|     | 4.3 Architecture Description 41                      |

|     | 4.3.1 Hardware 41                                    |

|     | 4.3.2 Software 43                                    |

|     | 4.4 Verification and Results 45                      |

|     | 4.4.1 Hardware Implementation 45                     |

|     | 4.4.2 Communication Speed 45                         |

|     | 4.4.3 Image processing 46                            |

|     |                                                      |

| _   |                                                      |

| 5   | GPU COMPUTER VISION SYSTEM 49                        |

|     | 5.1 Introduction 51                                  |

|     | 5.2 Spectrogram acquisition 52                       |

|     | 5.3 Processor optimisation 53                        |

|     | 5.3.1 Motivation 54                                  |

|     | 5.3.2 Description of the Operational L0 Processor 54 |

|     | 5.3.3 Performance 56                                 |

|     | 5.4 GPU acceleration 58                              |

|     | 5.5 Conclusion 60                                    |

|     | (.                                                   |

| iii | MODULAR COMPUTER VISION SYSTEM: QT5022 61            |

| 6   | MODULAR COMPUTER VISION SYSTEM 63                    |

|     | 6.1 Computer Vision Systems: Design Pattern 65       |

|     | 6.2 Modular Computer Vision System 66                |

|     | 6.3 Interfaces on a Modular Architecture 68          |

|     | 6.4 QT5022: a Modular Computer Vision System 69      |

|     | 6.4.1 Head 70                                        |

|     | 6.4.2 Body 71                                        |

| 7   | DATA FLOW 73                                         |

|     | 7.1 Sensor 75                                        |

|     | 7.2 Image Processing Pipeline 75                     |

|     | 7.2.1 Frame Grabber 76                               |

|     | - · ·                                                |

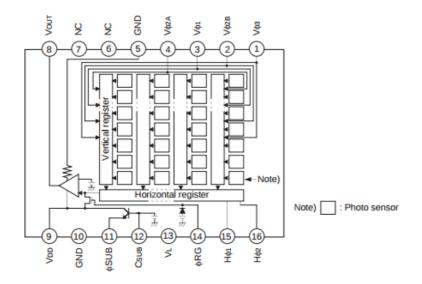

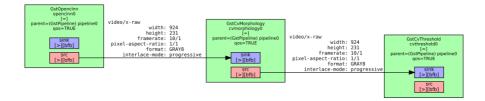

7.2.2 Pixel Readout 76 7.2.3 Frame bus 83 7.2.4 White Balance 84 XForm 85 7.2.5 7.2.6 Data Packer 89 7.2.7 DMA Engine 92 PCI bridge 7.2.8 94 7.3 Processing Unit 95 Video4Linux2 Input/Output 7.3.1 96 7.3.2 V<sub>4</sub>L<sub>2</sub> Control Interface 98 7.3.3 V4L2 Miscellanea 99 7.4 Acceleration Unit 100 OpenCL programming model 7.4.1102 OpenCL memory model 7.4.2 102 7.4.3 Camera Data Flow 102 8 HARDWARE 105 8.1 External Acquisition Accessories 107 Light Source 8.1.1 107 8.1.2 Flash Unit 110 8.1.3 Optics 112 8.2 Image Sensor 114 8.2.1 Sony ICX204 116 8.2.2 CMOSIS CMV 118 8.2.3 Andanta FPA320x256-C 120 8.2.4 Ulis UL 05 25 1-026 121 8.3 Image Processing Pipeline 122 8.4 Processing Unit 125 8.4.1 CPU 126 GPU 8.4.2 127 8.5 Hardware Monitor 127 8.6 Peripherals and Interfaces 128 8.7 Acceleration Unit 130 8.8 Interaction with other systems 134 8.8.1 PTP 134

8.9 Ethercat 136

| 9  | SOF              | TWARE  | 139                                       |  |  |  |  |

|----|------------------|--------|-------------------------------------------|--|--|--|--|

| -  | 9.1              | Kerne  |                                           |  |  |  |  |

|    |                  | 9.1.1  | Linux Development Model 142               |  |  |  |  |

|    |                  | 9.1.2  | Linux Device Driver Model 143             |  |  |  |  |

|    |                  | 9.1.3  | Video4Linux2 147                          |  |  |  |  |

|    |                  | 9.1.4  | Serial communication 153                  |  |  |  |  |

|    |                  | 9.1.5  | SPI 154                                   |  |  |  |  |

|    |                  | 9.1.6  | USB Gadget 156                            |  |  |  |  |

|    |                  | 9.1.7  | Other contributions 158                   |  |  |  |  |

|    | 9.2              | Non-v  | olatile Memory Provisioning 159           |  |  |  |  |

|    |                  | 9.2.1  | BIOS 159                                  |  |  |  |  |

|    |                  | 9.2.2  | Ethernet Card 159                         |  |  |  |  |

|    |                  | 9.2.3  | FPGA Flash 160                            |  |  |  |  |

|    |                  | 9.2.4  | Flash Unit 160                            |  |  |  |  |

|    |                  | 9.2.5  | Micro Four Thirds Module 161              |  |  |  |  |

|    |                  | 9.2.6  | Hardware Monitor 161                      |  |  |  |  |

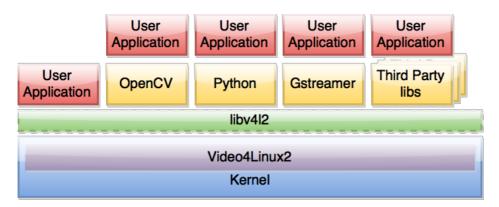

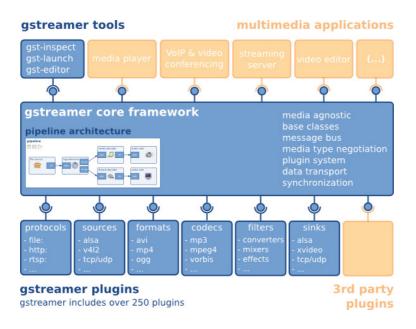

|    | 9.3              | Comp   | uter Vision Stack 161                     |  |  |  |  |

|    |                  | 9.3.1  | Video4Linux2 Utils - libv4l2 162          |  |  |  |  |

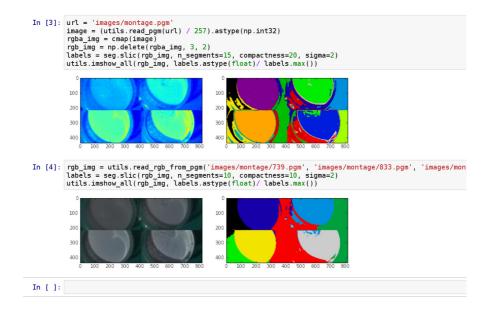

|    |                  | 9.3.2  | OpenCV 164                                |  |  |  |  |

|    |                  | 9.3.3  | Python 165                                |  |  |  |  |

|    |                  | 9.3.4  |                                           |  |  |  |  |

|    |                  |        | Third Party libraries 167                 |  |  |  |  |

|    |                  | 9.3.6  | -                                         |  |  |  |  |

|    | 9.4              |        | Applications and Libraries 169            |  |  |  |  |

|    |                  | 9.4.1  | Linux Distribution: Yocto Project 170     |  |  |  |  |

|    | 9.5              | -      | ic Drivers 171                            |  |  |  |  |

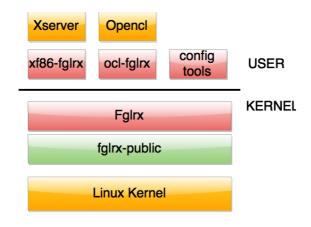

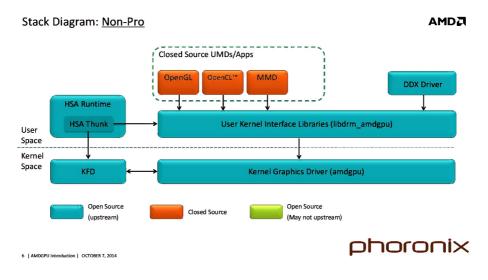

|    |                  | 9.5.1  | AMD Proprietary Display Drivers 171       |  |  |  |  |

|    |                  | 9.5.2  |                                           |  |  |  |  |

|    |                  | 9.5.3  | Beyond AMD Proprietary Display Driver 173 |  |  |  |  |

| 10 | APPLICATIONS 175 |        |                                           |  |  |  |  |

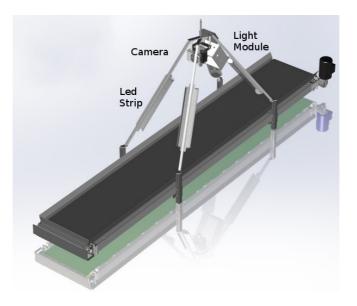

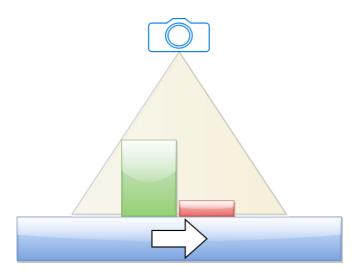

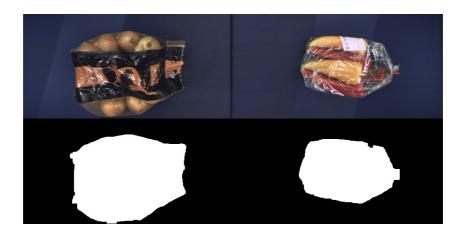

|    | 10.1             | -      | ll Potato Grader 177                      |  |  |  |  |

|    |                  |        | Image Acquisition 178                     |  |  |  |  |

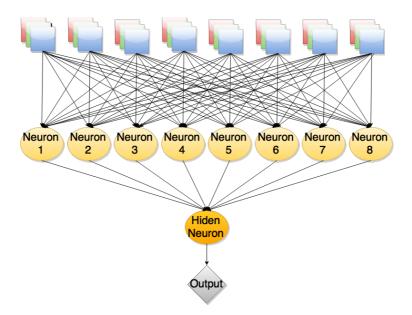

|    |                  |        | Multilayer Perceptron 179                 |  |  |  |  |

|    |                  | 10.1.3 | Imaging algorithm 181                     |  |  |  |  |

10.1.4 Data Flow 181

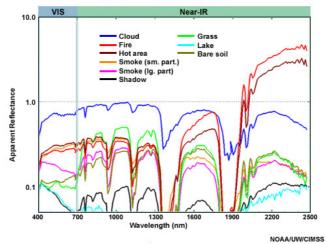

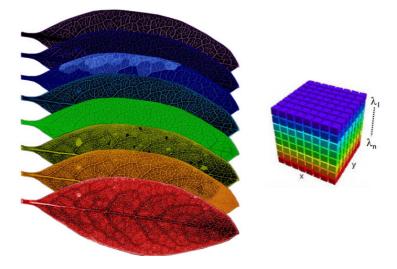

10.1.5 Results 182 10.2 Batch analyzer 183 10.2.1 3D reconstruction 184 10.2.2 Data Flow 185 10.2.3 Results 187 10.3 Checkweigher 188 10.3.1 Bag detection 189 10.3.2 Data Flow 190 10.3.3 Results 191 10.4 Hyperspectral camera 191 10.4.1 Hyperspectral cube 194 10.4.2 Results 195 iv conclusions 197 **11 CONCLUSIONS AND FUTURE WORK** 199 11.1 Contributions to Computer Vision Systems 201 11.1.1 Modular Computer Vision System 201 11.1.2 Xform 201 11.1.3 Open Source 202 11.2 System implementation: QT5022 202 11.3 Contributions 203 11.3.1 Publications 203 11.3.2 Open Source 205 11.4 Future Work 206 **12 CONCLUSIONES Y LÍNEAS FUTURAS** 209 12.1 Contribuciones a los sistemas de Visión por Computador 211 12.1.1 Sistema modular de visión por Computador 211 12.1.2 Xform 211 12.1.3 Software Libre 212 12.2 Implementación de la plataforma : QT5022 212 12.3 Contribuciones 213 12.3.1 Publicaciones 213 12.3.2 Software Libre 215 12.4 Líneas futuras 216

V APPENDICES 219

A CONTRIBUTIONS TO THE LINUX KERNEL 221

B CONTRIBUTIONS TO U-BOOT 293

- C OTHER CONTRIBUTIONS TO OPEN SOURCE PROJECTS 305

- c.1 Video4Linux2 Utils libv4l2 306

- c.2 OpenEmbedded / YoctoProject 308

- c.3 Clpeak 315

- c.4 FlashRom 316

- c.5 VideoLan Client 317

Bibliography 319

EPILOGUE 343

## ACRONYMS

- ABI Application Binary Interface

- AD Analog to Digital Converter

- ALU Arithmetic Logic Unit

- API Application Program Interface

- APU AMD Accelerated Processing Unit

- ASIC Application-Specific Integrated Circuit

- AXI Advanced eXtensible Interface

- BAR Base Address Registers

- BIOS Basic Input/Output System

- **BLOB** Binary Large OBject

- BRAM Block Random Access Memory

- CA Certificate Authority

- CCD Charge-coupled device

- **CDS** Correlated Double Sampling

- CMOS Complementary Metal–Oxide–Semiconductor

- **CDMA** Central DMA Controller

- CPU Computer Processing Unit

- CMOS Complementary Metal-Oxide Semiconductor

- **COTS** Commercial Off-The-Shelf

- DAC Digital to Analog Converter

- DMA Direct Memory Access

- **DSP** Digital Signal Processor

- EtherCAT Ethernet for Control Automation Technology

- **EEPROM** Electrically Erasable Programmable Read-Only Memory

- FIFO Fist In First Out

- FOURCC Four Character Code

- FPGA Field Programmable Gate Array

- FPN Fixed Pattern Noise

- FPS Frames Per Second

- GFLOP Giga FLoating-point Operations Per Second

- **Gib** Gigabit 2<sup>30</sup> bits

- **GiB** Gigabyte 2<sup>30</sup> bytes

- **GLORIA** Gimbaled Limb Observer for Radiance Imaging of the Atmosphere

- GPGPU General Purpouse Graphical Processing Unit

- GPIO General Purpouse Input Output

- GPU Graphical Processing Unit

- HD High Definition

- HDR High Dynamic Range

- HDL Hardware Description Language

- **IDE** Integrated Development Environment

- InGaAs Indium Gallium Arsenide

- I2C Inter-Integrated Circuit

- **IO** Input Output

- IOCTL Input/Output ConTroL

- **IP** Internet Protocol

- IRQ Interrupt

- JTAG Joint Test Action Group

- **Kib** Kilobit 2<sup>10</sup> bits

- **KiB** KiloByte 2<sup>10</sup> bytes

- LED Light Emission Diode

- LUT Look Up Table

- LVDS Low-voltage differential signaling

- MAC Media Access Control

- **MiB** MegaByte 2<sup>20</sup> bytes

- **Mib** Megabit 2<sup>20</sup> bits

- mmap Memory mapping

- NBIS NIST Biometric Image Software

- NDA Non-disclosure agreement

- NTP Network Time Protocol

- **OPB** On-chip Peripheral Bus

- **OpenCV** Open Source Computer Vision Library

- **OS** Operating System

- PC Personal Computer

- PCB Printed Circuit Board

- PCI Peripheral Component Interconnect

- PCIe PCI express

- **PIO** Programmed Input Ouput

- PLB Processor Local Bus

- PLC Programmable Logic Controller

- PTP Precise Time Protocol

- PWM Pulse Width Modulation

- RAM Random Access Memory

- RGB Red Green Blue

- SMBUS System Management BUS

- SOC Sytem On Chip

- SATA Serial AT Attachment

- **SPI** Serial Peripheral Interface

- TCP Transmission Control Protocol

- **UDP** User Datagram Protocol

- UART Universal Asynchronous Receiver/Transmitter

- **USB** Universial Serial Bus

- TV Television

- VB2 Video Buffer 2

- WOI Window Of Interest

Part I

## INTRODUCTION AND STATE OF THE ART

#

## INTRODUCTION

## INTRODUCTION

## Contents

| <ol> <li>1.2 Design Goals 7</li> <li>1.3 History of the Project 8</li> <li>1.4 Structure of the document 9</li> </ol> | 1.1 | Motivation 5              |   |   |

|-----------------------------------------------------------------------------------------------------------------------|-----|---------------------------|---|---|

|                                                                                                                       | 1.2 | Design Goals 7            |   |   |

| 1.4 Structure of the document 9                                                                                       | 1.3 | History of the Project 8  |   |   |

|                                                                                                                       | 1.4 | Structure of the document | 9 | 9 |

## 1.1 MOTIVATION

The first Charge-coupled devices (CCDs) were invented by Willard Boyle and George E. Smith on 1969 [WG70]. It took less than a decade for the industry to integrate them into their production chains [Ste79, PCM79, Kos79].

Since then, Computer Vision Systems have play a predominant role on the Industrial Processes; there are multiple logical reasons for this:

- There are processes that cannot be done with Manual Inspection because of the limits of the human perception: We cannot detect artifacts on the invisible bands [BAGM07], or inspect very small objects [RS06].

- Computer Vision Systems give more predictable results and a better error rate than Manual Inspections [MGS98].

- In the long term, a Computer Vision System is financially cheaper than Manual Inspection. A good example are the Optical Graders, with a payback period of less than a year [A/S15].

- Manual Inspection is a very repetitive maneuver than can lead to unhealthy working conditions for the operators [KK79].

Although Computer Vision Systems have evolved in performance and sensing capabilities, both Industry and Academia have felt short to met some of the expectations from the early pioneers of Industrial Computer Vision Systems. Gerald J. Agin in 1980 started his paper Computer Vision Systems for Industrial Inspection and Assembly [Agi80] with this phrase: *Custom-designed computer vision systems are being applied to specific manufacturing tasks. Current development may lead to general-purpose systems for a broad range of industrial applications.* In 2015, 35 years later, that general-purpose system still does not exist to much despair of engineers and researchers in the field.

In 1980, off-the-shelf hardware did not have the capabilities to conform a general-purpose system. The systems of that time were art pieces,

#### INTRODUCTION

formed by tailor made parts, targeted to an specific application and sold as a black box.

Nowadays, hardware is, by comparison to early 80s, hundreds of time more capable and manufacturers still sell their product as black boxes, even though they are formed by Commercial Off-The-Shelf (COTS) parts. In an interesting semantic paradox, it is worth observing that the word camera origins from the Latin term *Camera obscura* (Dark chamber).

Despite the predicaments on the power of hardware, Computer Vision Systems are installed in almost every production line of each market. What is the challenge or problem then? Is there a need of General-Purpose System? The reality is that the lack of that System is slowing down the overall progress in the field.

This situation is exacerbated by some idiosyncrasies of the research and development environments in the field: on one side there is the Academia, where almost each group has to create their own vision system from scratch, and there is no chance of sharing code and comparing results objectively. Therefore, academic groups develop Galapago Island type of paradigms that are difficult to transfer to Industry. On the other side is the Industry, which is very conservative when it comes to migrating to new systems, as the transfer involved heavy financial costs along with technological uncertainties.

If the society have reached an impressive level of automation without sharing resources, it is easy to dream where could it go with more powerful tools. However, if a Generic Computer Vision System would be such a important milestone, why it hasn't be proposed before?

It would be easy to blame the Industry: if a public standard would exist, the entry barrier to new competitors would be lower, and hence incumbent companies would lose their market share. The reality is that there are a lot of technical challenges on the development of a General Purpose System: there are just too many sensors and processing architectures.

This Thesis implements a novel Computer Vision System that can be used on almost any Industrial Application, regardless of what sensor or architecture they use. This system has been successfully used on a variety of products, and it has been installed on more than 200 locations around the world.

The major contribution of this System and the reason why it is so versatile is that it is based on a modular structure: The black box has been opened and divided into its main parts. On the hardware side, the components are connected with standard industrial interfaces and on the software side there has been an intense work with the Open Source Community to extend their current interfaces to fulfill the needs of the Industrial Computer Vision.

### 1.2 DESIGN GOALS

The purpose of this Thesis is the implementation of a generic Computer Vision System for Industrial applications.

The requirement analysis will be done on a very practical way: by the implementation of three custom Computer Vision Systems.

The final system should fulfil the following requisites:

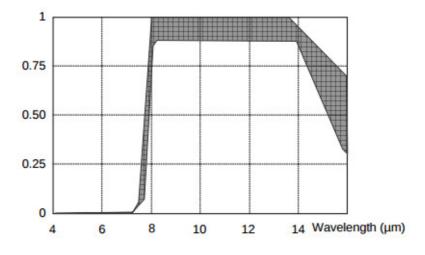

- Compatibility with a wide range of sensors: From standard sensors, such as CCD or Complementary Metal-Oxide Semiconductor (CMOS) to more rare sensors, such as Indium Gallium Arsenide (InGaAs) or Microbolometer.

- 2. Support for acceleration hardware like Graphical Processing Units (GPUs) or Field Programmable Gate Arrays (FPGAs).

- 3. Open Source software stack with a good collection of Image Processing libraries and use of standard interfaces.

All the changes to the Open Source stack should be contributed back to the Open Source community.

The system will be validated against as many applications as possible, preferable in real-life products.

## 1.3 HISTORY OF THE PROJECT

When a Thesis takes eight years to complete from the day the student obtained his Master of Advanced Studies it deserves a justification:

The initial project of my Thesis was titled: *Identification System based on System-on-Token extensible with certificates* which was granted by the Spanish Ministry of Education and Science.

Finding the right platform for developing that Thesis resulted to be a very difficult challenge. Almost immediately, I realized that the platform developed for my Master of Advanced Studies was not a good candidate, so I moved on to a Sytem On Chip (SOC) that seemed to fulfil my requirements.

Unfortunately, years later I hit a performance wall that I could not overcome; the platform was not powerful enough.

When I was looking for a newer and more powerful platform I realized that each of them required a reimplementation of my application: I had to throw away all the hardware customizations that I did, and most of the software developed.

After my visit to Forschungszentrum Juelich, I learnt two things: First of all, I realized that I have better aptitudes on System Architecture than in Biometry. And then, I discovered that the German Research Centre was facing the same issues as me: They could not find a Computer Vision System that could work on all their systems.

After a very intense internship, I decided to move the focus of my Thesis from Biometry to System Design, and I was lucky enough to be part of a Research Group, HCTLAB, with experience on Generic Robotic Platforms, and there was a lot of ideas from that field that could be useful here.

My new goal was to make a real platform, not a prototype, and soon I discovered that there was too much food on my plate: I needed help and funding, which my University could not provide.

On my journey I met Qtechnology, which had a similar vision and could give me all the support that I needed. I was very lucky to join their team in 2010.

During my job in Qtechnology I realized how difficult it is to make a commercial product, and also how difficult was to complete a Thesis while working on a full-time job.

It took me five years, two completely different designs, and thousands of hours to complete a Computer Vision System that could be used on my original Thesis project. Maybe one day I will make a second thesis with the original title, using the platform developed in this Thesis, I cannot think of a better way to close the circle.

And now, let's go back to the present Thesis.

#### 1.4 STRUCTURE OF THE DOCUMENT

This document is divided in five parts:

- 1. The first part is dedicated to the Introduction (this chapter) and State of the art (chapter 2).

- 2. On the second part three different custom Computer Vision Systems are described: one based on a System on Chip (chapter 3), another based on an FPGA (chapter 4) and the final one based on a CPU/GPU (chapter 5). The development of these systems allowed the author to gather the requirements of the final system.

- 3. On the third part, the proposed Computer Vision System is described: An introduction of the platform is given on chapter 6, then the dataflow is described on chapter 7, to continue with a detailed description of the hardware on chapter 8 and finalize with the software modules on chapter 9.

- 4. The fourth part is dedicated to the conclusions and future work, there is an English version on chapter 11, and Spanish version on chapter 12.

- 5. The fifth (and final) part of this document belongs to the appendices, where the contributions to the Kernel (chapter A), U-boot (chapter B) and other Open Source projects (chapter C) are detailed.

## INTRODUCTION

The document ends with a list of references.

## 2

## STATE OF THE ART

This chapter gives an overview of the current platforms for Industrial Computer Vision Systems. The state of the art of more specific topics, such as sensing technology or light sources are detailed on the main matter chapters of this document, in order to have self-contained, and easier to read chapters.

## Contents

| 2.1 | Definition 13                                    |  |  |  |  |  |

|-----|--------------------------------------------------|--|--|--|--|--|

| 2.2 | Industrial Computer Vision 14                    |  |  |  |  |  |

| 2.3 | Computer Vision Stages 14                        |  |  |  |  |  |

| 2.4 | Computer Vision Computation Architectures 16     |  |  |  |  |  |

|     | 2.4.1 Digital Signal Processors 16               |  |  |  |  |  |

|     | 2.4.2 Field Programmable Gate Arrays 17          |  |  |  |  |  |

|     | 2.4.3 Cluster Computing 17                       |  |  |  |  |  |

|     | 2.4.4 General Purpose Graphics Processor Unit 17 |  |  |  |  |  |

| 2.5 | Computer Vision Platforms 18                     |  |  |  |  |  |

|     |                                                  |  |  |  |  |  |

#### 2.1 DEFINITION

Figure 2.1.: SRI Vision Module

#### 2.1 DEFINITION

There are multiple definitions of Computer Vision, perhaps the most cited is the one by Dana H. Ballard and Christopher M. Brown, in 1989: "*The construction of explicit and meaningful descriptions of physical objects from images*" [BB82].

Reaching to that definition was not an easy job: in 1980, Gerald J. Agin, explicitly said in his paper, Computer Vision Systems for Industrial Inspection and Assembly [Agi80] that "It is not at all clear what the term "computer vision" means".

Figure 2.1 shows one of those firsts Computer Vision System [Bol79].

What it was clear from the very beginning was that this field was going to have a great economical impact for the industry. A.M. Wallace in 1988 projected a revenue of 1200 millions of dolars for 1994: a 2000% increase in 7 years.

Their projections were correct, in 2015 Computer Vision is ubiquitous. It is found in medicine [SC13], army [BMBJ15], surveillance [APO14], food industry [DC<sup>+</sup>12], electronic manufacturing [Pau12], space research [MMJ<sup>+</sup>07], road monitoring [SD01] and self-driving cars [Gui11], just to mention a few of the fields where it is present.

### 2.2 INDUSTRIAL COMPUTER VISION

Industrial Computer Vision is the application of the Computer Vision principles in the Industrial processes.

This is a particularly interesting market because the applications are cost tolerant and more focused in top-performance than any other application [Nieo7]. The cost tolerance is due to the fast return of investment in Industrial Computer Vision [Gunoo, A/S15]. And the top-performance focus is due to the increased awareness and sophistication of the consumers[BS04, SB00].

The capabilities of an artificial vision system go beyond the limited human perception and deliver much more deterministic results [CAM<sup>+</sup>11]. A good example of these demands is the corn kernel analyzer from the United States Department of Agricultural Research Service [Peao9], with a throughput of 75 kernels per second.

Aside from the primary applications of Computer Vision, i.e. grading, sizing, defects detection; the objective results from an automatic system can be used as input for a data mining system in order to improving the production of raw materials [web15] (Figure 2.2).

#### 2.3 COMPUTER VISION STAGES

Almost all the Computer Vision Systems follow the same steps: acquisition, pre-processing and perception:

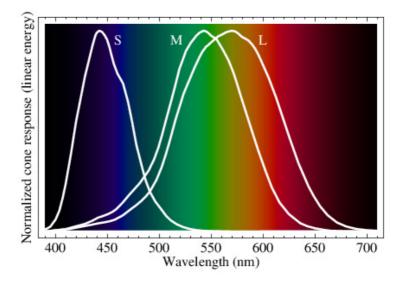

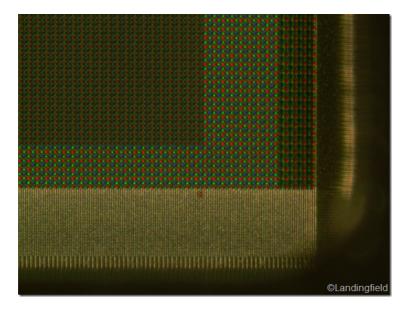

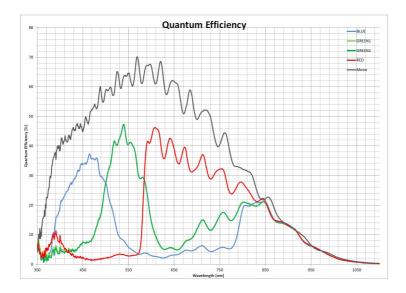

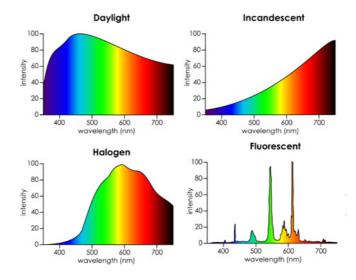

- Acquisition: In this step an imaging sensor is used to capture an image. Depending on the nature of the scene, different technologies can be used, such as: CCDs [Sunoo], CMOSs [ASo5], InGaAss [AL10] or Microbolometers [YMB<sup>+</sup>03]. Chapter 8 gives a more detailed overview of the sensors technologies.

- Pre-processing: The image is digitally enhanced using image processing algorithms, such as white balance Fixed Pattern Noise (FPN) correction, compensation of geometric defects, et cetera. Some sensors can do some of these corrections on the fly [RVDCJG<sup>+</sup>08], but

### 2.3 COMPUTER VISION STAGES

Figure 2.2.: Newtec Web Services Data Mining

this processing is usually done on auxiliary hardware like FPGAs [WK11], or in software [B<sup>+</sup>00].

3. Perception: The interpretation of a calibrated image that guides the decisions of the computer Vision. This usually follows two steps: Segmentation and Pattern Recognition.

Figure 2.3 from [TCYT12], shows those 3 steps, on the first image a fingerprint is acquired, on the second the image is pre-processed to enhance the minutiae and on the last one, the minutiae are detected.

The image processing algorithms involved in the pre-processing and perception are very demanding and heterogeneous [BCJK05]: On one hand, low-level image processing operations such as interpolation, segmentation and edge enhancement are local, regular and require vast amounts of bandwidth. On the other hand, high-level operations like classification, path planning, and control may be irregular and consume less bandwidth.

Figure 2.3.: Steps in Computer Vision

Sensor's resolution have increased exponentially on the last years. Nowadays it is common to use sensors with tens of megapixels at hundreds of frames per second [HKLP09].

These extreme and heterogeneous requirements make the Computer Vision, one of the biggest challenges of Computer Science.

# 2.4 COMPUTER VISION COMPUTATION ARCHITECTURES

The high demands of Computer Vision algorithms can only be fulfill with the help of special hardware. These are the most relevant platforms from the literature:

# 2.4.1 Digital Signal Processors

A Digital Signal Processor (DSP) is a specialized processor with an architecture specially designed for Signal Processing. Multiple Multiply-and-Carry operations can be done in parallel with a fraction of the power consumption of a General Purpose Computer Processing Unit (CPU).

They were quite popular on the 90s for Computer Vision and nowadays they still have a niche of systems that require a lot of stability  $[HRJ^+o5]$  or where the price is a deciding factor  $[BDM^+o6]$ .

## 2.4 COMPUTER VISION COMPUTATION ARCHITECTURES

## 2.4.2 Field Programmable Gate Arrays

An FPGA is a chip formed by millions of programmable logic blocks that can be configured to emulate almost any circuit.

In the last years, the number of programmable logic blocks on the FPGAs, and their maximum working speed have increased exponentially.

Thanks to the inclusion of DSPs as programmable logic blocks, they are taking over the market of the DSPs [SB09].

Xilinx, one of the main FPGA manufacturer, have recently released a series of cores and tools for the development of Computer Vision Systems [Vis13].

There are plenty of examples of FPGAs used on Computer Vision [BB14]: detection of potato greening [Sin14], real time stereo vision [WVH97], corn kernel analysis [Peao9] or pedestrian detection [HSH<sup>+</sup>13], just to cite a few examples.

# 2.4.3 Cluster Computing

Clusters are a group of standard computers working towards the same task.

They are mainly used on off-line image processing algorithms like [MGMEPP<sup>+</sup>11] or [KGWK96]. The reason for this is the great latency introduced by the load distribution among their nodes.

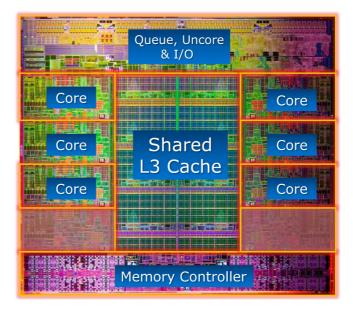

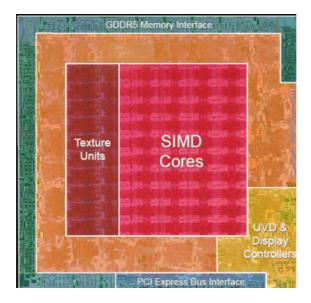

# 2.4.4 General Purpose Graphics Processor Unit

General Purpouse Graphical Processing Unit (GPGPU) is the use of graphic cards, i.e. GPU, for general purpose problems. The advantage of using GPUs is their great parallelism. They are becoming very popular platform due to its availability.

GPGPU started as a hack, an attempt to exploit the graphic card shaders for something else than image rendering [LMo1]. The industry then realized of the great potential of this technology and released new

## STATE OF THE ART

programming languages for accessing the GPUs hardware on a more structured way [DWL<sup>+</sup>12].

Soon after the development of CUDA and OpenCL, Computer Vision Systems that made use of the GPUs started to proliferate. Just to cite some examples, GPUs are used today in Aerial photography [Ver11], Face detection [KN12] or even cloud tracking and reconstruction [GGKP08].

Thanks to the popularity and performance of OpenCL, standard Image Processing libraries like OpenCV [Gas14] and video encoders like x264 [MM10] are making use of the computing power of the GPU seamlessly.

## 2.5 COMPUTER VISION PLATFORMS

A computer Vision Platform is the combination of an Imaging Sensor, a Computation Unit and the software required to process the image flow.

The first platforms were composed by an COTS image sensor connected to a computation unit. The interface between the image sensor and the computation unit could be a proprietary framegrabber [Kumo8] or a standard bus like Firewire[RTGM03], USB [MA04] or, more recently, Gigabit Ethernet in the form of GenIcam [Fei15].

On that type of platforms, the functionality of the sensor is limited to the usually poor Application Program Interface (API) provided by the manufacturer. Advanced features such as External Trigger or custom High Dynamic Range (HDR) cannot be done. Also, some of the standard interfaces have latencies of one or more frames.

There are other type of platforms, denominated smart cameras, where the sensor is integrated with the Computation Unit. On the literature the most common smart cameras are based on FPGAs [STo7b, SAW<sup>+</sup>08, ZWO<sup>+</sup>11], with some exceptions based on DSPs [BRSo4] and SOCs [RRNo2].

These systems usually provide better control of the sensor and there is almost no latency on the data capture. The biggest downside is that they behave like a black box: neither the sensor nor the computing unit can be replaced and despite the fact that they usually run Linux or an embedded version of Windows, the User API is limited to whatever the manufacturer has decided to expose.

There are only three smart cameras on the literature that do not follow the black model concept (Figure 2.4):

- Elphel camera [Filo3]: FPGA based smart camera, where all the components are Open Software and Hardware.

- Standford's Frankencamera [ATP<sup>+</sup>10]: Multiplatform Linux Based camera with focus in custom trigger timing and accurate flash. Two versions are available, one based on the Nokia N800, and another one based on an Elphel design.

- Carnegie Mellon University CMUCam [RRNo2]: Open Source smartcamera designed to provide Computer Vision capabilities to other devices like Arduino or the Raspberry Pi. It has a very limited set of computer vision algorithm, mostly color detection programs.

Unfortunate, none of them uses the current Linux video acquisition system (Video4Linux2) to support their extra capability: instead, they implement their own libraries.

# STATE OF THE ART

Figure 2.4.: Open SmartCameras Top Left: Elphel, Bottom Left: CMU Cam, Center Right: Frankencamera

Part II

CUSTOM COMPUTER VISION SYSTEMS

# 3

# EMBEDDED SYSTEM ON CHIP COMPUTER VISION

This chapter describes a Computer Vision System based on a SOC running on a commercial device.

A common biometric algorithm, designed for workstations has been selected as the target algorithm. All the optimizations implemented for fitting the algorithm into the SOC will be described with the impact on the accuracy of the algorithm.

| 3.1 | Introduction 25                       |

|-----|---------------------------------------|

|     | 3.1.1 Classical Biometric Systems 25  |

|     | 3.1.2 X.509 digital certificates 28   |

| 3.2 | System-on-Token 29                    |

|     | 3.2.1 System on Token Architecture 29 |

|     | 3.2.2 Transactions 31                 |

| 3.3 | Implementation 32                     |

|     | 3.3.1 Device Selection 32             |

|     | 3.3.2 Biometric Module 33             |

|     | 3.3.3 Certificate Module 35           |

| 3.4 | Dataflow 35                           |

| 3.5 | Conclusions 36                        |

## 3.1 INTRODUCTION

In some scenarios, users need to be authenticated by "what they are" instead of "what they own/know". Although biometric verification has many years of life, its implementation in the real world as the substitute for keys/passwords is not so extended.

Formal biometric systems presents a critical problem: biometric patterns cannot be revoked, as the user is born and lives with them. If they are compromised, an impostor could use them to exploit any working system the user has been granted.

Furthermore, there is no biometric technique that can be used for the whole population. Even techniques as mature as fingerprint recognition can't be used universally because of physical problems (like amputations) or sensing problems.

Also, many people don't want to be authenticated by biometrics, they consider it an attack to their privacy.

This chapter introduces a new biometric architecture, based on an Embedded Computer Vision System and denominated System-on-Token, that overcomes all these problems, giving the user full control over his personal data. The implementation discussed on this chapter runs on a commercial System on Chip device, a N800 as shown on Figure 3.1.

## 3.1.1 Classical Biometric Systems

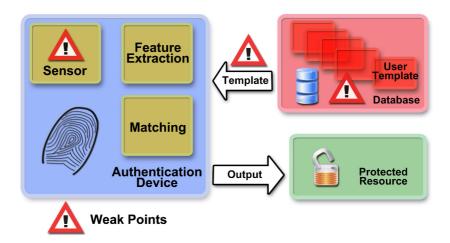

The typical biometric system consists on a huge biometric database and one sensor per application/access. On this scenario, the biometric profiles can be compromised in many points as shown on figure 3.2.

The most obvious attack to gain the biometric patterns from the user, is the compromise of the biometric database. To overcome this problem, the templates on the database should be securized [JNNo8], but unfortunately this process affects the accuracy of the system.

Other possible attack vector are the sensors of the system, which could be manipulated or even replaced with malicious devices to steal the personal data.

## EMBEDDED SYSTEM ON CHIP COMPUTER VISION

Figure 3.1.: N800

Figure 3.2.: Classical Architecture

## 3.1 INTRODUCTION

Figure 3.3.: Match-on-Token Architecture

Finally, the biometric patterns could be sniffed or spoofed as they travel through the network,

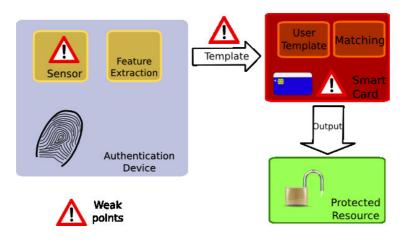

To overcome the weak points of the classical biometric architecture other works [MGPCo<sub>3</sub>, ISKo<sub>1</sub>] propose a Match-on-Token (Fig 3.3) architecture. On this architecture, the user keeps a token with his biometric data. This architecture removes the attack vectors on the database and the network, but, the user still needs to use a biometric sensor that does not control and could be manipulated.

To overcome this problem, the industry has introduced the Sensor-on-Token architecture, where the user custody the sensor and the biometric profile usually on the form of a smartcard with a fingerprint sensor [Todo2]. This solution removes the implied trust on any sensor but also present some problems: The user has to trust the security of the card.

There is almost no information about what algorithms are working on the card and the quality of them. These systems are developed to be as obscure as the bank smart cards, whose insecurity has been demonstrated earlier [DMo7].

Also these cards can only support a small set of biometric modalities due to the strong restrictions on their size.

## EMBEDDED SYSTEM ON CHIP COMPUTER VISION

In 2002 there were at least 15 companies developing smart cards with sensing/matching capabilities [Todo2], 13 years later, none of these companies have overtaken a significant portion of the banking card market.

Other authors have worked the idea of a System-on-Token [KMW<sup>+</sup>06, MKS<sup>+</sup>06] architecture, where the biometric sensor, network interfaces and biometric data lives on an embedded device custodied by the final user. Unfortunately none of these systems can be audited as a whole.

# 3.1.2 X.509 digital certificates

Nowadays, many official formalities can be done remotely thanks to the digital certificates [AF99]. An official organization issues an RSA certificate that allows the user to sign digital transactions anywhere in the world with a computer. This digital signature has the same legal validity as the physical one [GZ03].

The certificates are usually contained in a smart-card or in a passwordprotected file, this kind of security model follows the classical idea of "what you have" and "what you know".

These certificates follows an asymmetric cryptography model [JKo3]. A certificate is composed by a pair of keys, a public (P()) and a private one(Q()). Any document (x) encrypted with the public key (P(x)) can only be decrypted (Q(x)) using the private key and vice versa(P(Q(x)) = x = Q(P(x))). The private key is maintained by the user and the public key is released to the public. There is no way of calculating one key using the other ( $\nexists f(x) | f(Q) = P \forall P, Q$ ).

This cryptography model can be also used for signing documents. To obtain signature (*S*) of a document (*x*), the document is firstly hashed (*H*()) and then encrypted with the private key of the user (S = Q(H(x))). A signature can be verified using the public key of the signer (P(S) = H(x)). Any document signed by the user cannot be repudiated by him / her and the content cannot be modified by a third party.

## 3.2 SYSTEM-ON-TOKEN

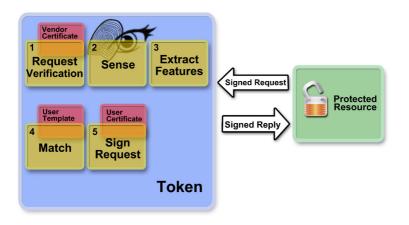

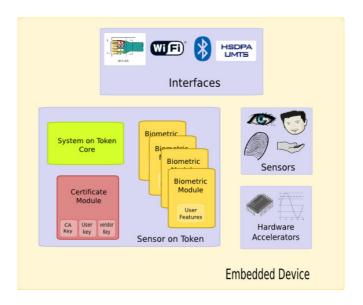

Figure 3.4.: System-on-Token Architecture

# 3.2 SYSTEM-ON-TOKEN

A Biometric System-on-Token (Figure 3.4) consists on a token carried by the user which can realize all the operations involved in a complete biometric system:

- 1. Sensing a Biometric Modality.

- 2. Extract the features.

- 3. Match the extracted features with other reference features.

The Token should also be able to communicate with the outside world in a secured and authenticated way, providing the user information about the ongoing transactions. The output of the transaction is a signed reply.

System-on-Token is a step further than Match-on-Token and a natural evolution of Sensor-on-Card.

# 3.2.1 System on Token Architecture

Figure 3.5 shows the main parts of a System on Token architecture:

## EMBEDDED SYSTEM ON CHIP COMPUTER VISION

Figure 3.5.: System-on-Token Architecture

- Network interfaces: such as Ethernet, WIFI, Bluetooth, 4G...

- Sensors: Biometric sensors: such as fingerprint scanner, eye scanner, cameras, microphones..

- Hardware Accelerators: used to speed up the Cryptographic algorithms and the imaging algorithms.

- System on Token core: handles the external requests and interacts the other modules.

- Certificate module: Handles the user private and public key as a well as the public key-chain.

- Biometric module: senses, extracts features and matches the biometric patterns.

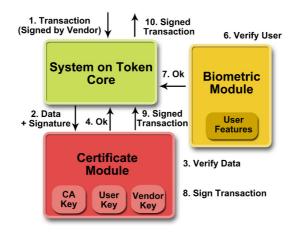

Figure 3.6.: Transaction

# 3.2.2 Transactions

Transactions are the basic operations of the System and have the same legal validity as a physically signed document between the vendor and the user.

The vendor starts the transaction sending a request to the user via any of its interfaces (Fig. 3.6). This transaction is processed by the device which verifies the identity of the vendor and discards the request if the key from the vendor is not trusted.

The user receives all the relevant information of the transactions and if he / she wants to continue with the transaction starts one of the biometric modules.

The biometric module verifies the identity of the user and unlocks the digital key of the user.

The key is used to sing the transaction, which is send back to the vendor.

In this process, no biometric parameters or certificate leaves the device / user.

# 3.2.2.1 Other operations

The device allows adding more vendor keys and other biometric modules, in a secure fashion. All these processes require the active interaction from the user.

# 3.3 IMPLEMENTATION

In order to implement the System-on-Token architecture on a embedded device there are some important points to take into account.

- Integration of the sensor in the device: Nowadays, it is common that that manufacturers add biometric sensors to their devices, but this is not a mandatory requirement for the selection of a platform, standard cameras might be used for biometry[LLKK05] or external sensors might be used via Universial Serial Bus (USB) On the Go or Bluetooth interfaces.

- 2. Integration of the Biometric Module into the system: Biometric algorithms are usually very computationally demanding. The platform should provide the required performance for a smooth user experience.

- 3. Integration of the Certificate Module in the device: New processors include cryptographic extensions for accelerating common algorithms.

- 4. Open Source: Drivers / Operating System (OS): The proposed architecture requires that the whole system can be audited, this can only be achieved by the use of Open Source.

# 3.3.1 Device Selection

For this implementation, a Nokia N800 has been selected. This device runs a Linux-based distribution [ST07a] that can be audited and modified. The hardware is based on a Texas Instruments Omap SOC, composed by a mixed ARM+DSP solution.

This SOC is specifically design for providing a high performance on signal processing algorithms, thanks to its integrated DSP; at the same time as it has a low power profile when it is in standby. This SOC is usually found on mobile phones or internet tablets.

## 3.3.2 Biometric Module

In order to provide a comparable result, the reference implementation for fingerprint processing from the National Institute of Standards and Technology has been used [GWMW01].

The NIST Biometric Image Software (NBIS) software consists on two main parts: Feature extraction (*mindtct*) and feature matching (*bozhort*<sub>3</sub>). It is completely developed in C/C++ and its source code can be obtained upon request from the NIST.

The initial steps for using the software on the device have been to port the code to ARM, this required taking care of the endian dependent parts of the code.

The performance of the module has been measured with a custom database consisting on 36 fingerprints from different users. These images have been obtained with an optical sensor, Biometrika FX2000, with USB connectivity. This sensor has been previously used on the BIOSECUR-ID database [GFOG<sup>+</sup>07].

In order to provide a good user experience, the goal of the biometric module was to be able to process a fingerprint under 2 seconds.

## 3.3.2.1 Feature Extraction

The *mindtdt* submodule finds out the minutiae of a fingerprint using an image as the input, it is the most computationally expensive component of the NBIS software.

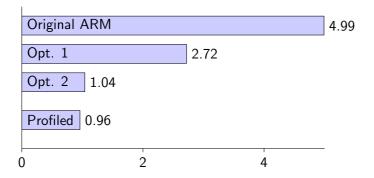

The ARM port of NBIS, developed for this project, took 5 seconds of processing time per fingerprint.

## EMBEDDED SYSTEM ON CHIP COMPUTER VISION

Figure 3.7.: Feature extraction time, in seconds (less is better) Original is the original version ported to ARM. Opt 1 is the ported version with the standard optimization flags. Opt 2 is the ported version with the best combination of compiler flags. Profiled is Opt 2 with the code optimized after profiling.

An initial optimization was done experimenting with the different compilers flags. This task achieved a speedup of 471%.

A second optimization analyzed the critical paths of the code using a profiler. Two functions were identified and optimized: *dirbinarize* contained divisions that could be substituted with binary operations and *math\_first\_pair* had a linear search that could be substituted by a hash search. All of these changes did not affect the accuracy of the algorithm and provided another speedup of 8.5%.

Figure 3.7 shows the speedup from the different optimizations.

# 3.3.2.2 Matching

The *bozorth*<sup>3</sup> module compares two minutiae files obtained with the previous module and gives a score determining their similarity.

Once ported to ARM, and compiled with the best combination of compiler flags it only needs around 0.092 seconds to compare two minutiae files.

| Function                   | Time (in secs) |  |

|----------------------------|----------------|--|

| Hash & Sign 100 bytes      | 0.13           |  |

| Hash & Sign 1000 bytes     | 0.14           |  |

| Hash & Sign 10000 bytes    | 0.14           |  |

| Hash & Sign 100000 bytes   | 0.15           |  |

| Hash & Sign 1000000 bytes  | 0.30           |  |

| Verify 100 bytes           | 0.02           |  |

| Verify 1000 bytes          | 0.03           |  |

| Verify 10000 bytes         | 0.03           |  |

| Verify 100000 bytes        | 0.03           |  |

| Verify 1000000 bytes       | 0.12           |  |

| Verify a X.509 certificate | 0.07           |  |

Table 1.: Open SSL Speed

# 3.3.3 Certificate Module

The Certificates are handled by OpenSSL [VMCo2], an open source implementation of the most common Cryptographic systems, including SSL, X509, SMIME and DSA/RSA. This software has been selected due to its broad adoption and the availability of its code.

Different tests has been performed to find out the time needed for validating a certificate, validating a transaction and signing a transaction. All the tests have been realized using an official X.509 Spanish Signature from the FNMT (Spanish Bureau of Engraving and Printing). Results are shown on table 1

## 3.4 DATAFLOW

This section describes the dataflow of the system from a Computer Vision System point of view.

• The user request via USB a new frame to the sensor.

## EMBEDDED SYSTEM ON CHIP COMPUTER VISION

- The frame is acquired by the sensor and transmitted via USB bulk transfers to the main CPU.

- The CPU launches the Feature Extraction program, producing a list of minutiae.

- The minutiae are matched against the user profile.

- If the profile is properly matched, the certificate is decrypted.

- The transaction is signed and returned to the vendor.

- All the memory is overwritten to avoid cold memory attacks.

# 3.5 CONCLUSIONS

The proposed system provides a solid alternative for credit cards and a easy way of hardening electronics transactions security with the use of biometry. The computation capabilities of the embedded devices are used to protect a standard X.509 user certificate, using any biometric modality selected by the user.

The biometric parameters of the user and his personal certificate never leave the embedded device reducing the attack vectors. All the system is based on Open Technologies that can be audited by third parties. This platform can be integrated in existing X.509 systems with minor changes.

When considering the use of this Computer Vision System in other applications, there are some downsides to consider. The most obvious problem is the low availability of sensors, the platform is limited by the SOC connectivity, which only has a small selection of sensors focused on consumer electronics.

The different parts of the system cannot be updated, as they are part of a SOC, if more performance or even more memory is required, the whole platforms needs to be replaced, discarding part of the code.

The only accelerator available on the system is the integrated DSP, which lacks a good development environment. Applications need to be rewritten to take advantage of the DSP, which is mainly targeted to multimedia decoding / encoding.

# 4

# FPGA COMPUTER VISION SYSTEM

This chapters describes a custom Computer Vision System with hardware and software preprocessing capabilities based on an FPGA with an embedded PowerPC processor, all running Linux.

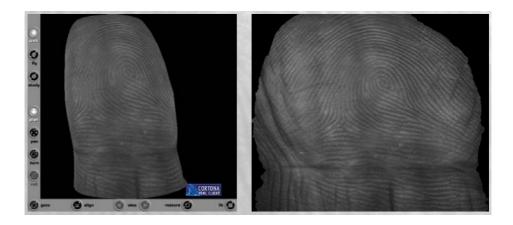

This implementation has been used on a commercial 3D fingerprint scanner.

## FPGA COMPUTER VISION SYSTEM

# Contents

| 4.1 | Introduction 39                  |  |  |

|-----|----------------------------------|--|--|

| 4.2 | FPGAs with embedded CPU cores 39 |  |  |

| 4.3 | Architecture Description 41      |  |  |

|     | 4.3.1 Hardware 41                |  |  |

|     | 4.3.2 Software 43                |  |  |

| 4.4 | Verification and Results 45      |  |  |

|     | 4.4.1 Hardware Implementation 45 |  |  |

|     | 4.4.2 Communication Speed 45     |  |  |

|     | 4.4.3 Image processing 46        |  |  |

| 4.5 | Conclusions 47                   |  |  |

## 4.1 INTRODUCTION

Traditional Fingerprint scanners acquire the images either by swiping the finger over a linear sensor or by pressing the finger against a planar sensor. This acquisition presents some problems: The minutiae are obtained from only a small part of the finger, i.e. not nail-to-nail, and the part analyzed is deformed by the pressure against the sensor, producing artifacts on the image.

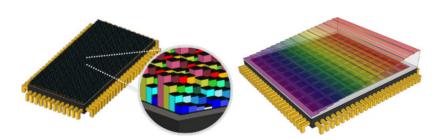

This is solved with the use of touch-less 3D image sensors [PCo9]. These sensors can produce a nail to nail fingerprint image as well as a 3D model of the whole finger (Figure 4.1), all acquired without deforming the finger. Such sensors have very high demands in terms of number of imaging sensor, resolution and computation power that COTS computer vision systems can not fulfil for the following reasons:

- 1. There is only a reduced selection of sensors available.

- High resolution cameras with network connectivity usually only deliver compressed images, which, destroys the information from the fingerprint sweat pores, usually referred as level-3 features [JCD07].

- 3. COTS are non auditable black boxes, this is a major concern in the development of safety equipment.

- Remote cameras usually lack preprocessing capabilities, which are needed to meet the timing requirements of a user-friendly product.

## 4.2 FPGAS WITH EMBEDDED CPU CORES

Image processing can be done via hardware or software.

Software processing [FSo5], consist on the analysis of an image by a CPU that is usually allocated on the main memory of the device. The high flexibility of the CPU allows an easy development of the algorithm

## FPGA COMPUTER VISION SYSTEM

Figure 4.1.: 3D fingerprint

and a very dynamic workflow. On the other hand, the software application requires a lot of time to process linearly the huge amount of data that comes from a sensor.

Hardware processing consist on the use of specialized chips, such as Application-Specific Integrated Circuits (ASICs) or FPGAs [SHo6a, LTOo5] that process the images on the fly. They provide very high framerates at the cost of a very complex and expensive development process.

The best from both worlds, software and hardware processing, can be achieved via an heterogeneous design. The initial designs that followed this heterogeneous methodology [Gaio3] were build around an FPGA with soft CPU cores, such as Microblaze[Xilo6] or LEON [TAKo6]. The main problem of such systems is the limited performance of the soft-core CPU and the great amount of FPGA resources required by them.

To overcome this problems, the FPGA manufacturers are introducing new families of FPGA with embedded hard-core CPUs, such as the Kintex or Virtex FX from Xilinx. These systems have become the state-ofthe-art in high-end development network devices [vdBWo5, HEo5] and are entering the Computer Vision market.

# 4.3 ARCHITECTURE DESCRIPTION

In this section, the architecture will be described, including hardware and software elements.

# 4.3.1 Hardware

# 4.3.1.1 Sensor

The noise ratio and resolution imposed by the requirements the final product could only be fulfilled by one Image Sensor: the BCI4-6600 [Veco6], from Vector International, a monochromatic 2208 x 3000 CMOS sensor. It is capable of producing 8, 10 and 12 bit depth images at a 40 MHz pixel rate (aprox 5.5 frames per second). The sensor was interfaced via a proprietary parallel interface.

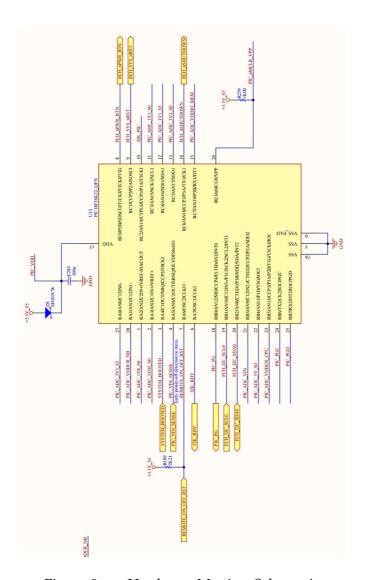

# 4.3.1.2 FPGA

At the time of developing this system, the best option of FPGA with embedded CPU was the Virtex 4 FX family. Each chip is composed by:

- One or two PowerPC 405 hard-cores.

- One or two TEMACs hard-cores.

- A reconfigurable area, i.e. FPGA fabric.

The PowerPC is used to control the whole device, although it might look like an outdated processor, its use in combination with co-processors can deliver enough performance for the project.

The TEMACs are used for connecting the System to a Gigabit Ethernet network, giving a maximum theoretical bandwidth of 1000 Megabit  $2^{20}$  bits (Mib)/sec, enough for high resolution video at high framerates and RAW format.

The FPGA fabric is used for buses, glue logic to the camera and other cores such as serial port, timers, etc.

## FPGA COMPUTER VISION SYSTEM

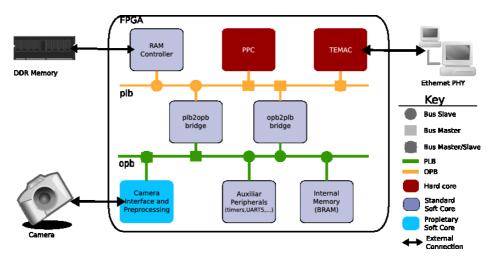

Figure 4.2.: FPGA design

# 4.3.1.3 Buses & Specific Peripherals

The PowerPC is accompanied by a set of cores used to access the external peripherals and pre-process the image. The cores are accessible via two different buses: Processor Local Bus (PLB) and On-chip Peripheral Bus (OPB). PLB is designed for high speed peripherals such as the TEMAC or the Direct Memory Access (DMA) engines and OPB is a much simpler bus used for low speed devices such as serial ports or General Purpouse Input Outputs (GPIOs).

On this design, the Xilinx cores have been used wherever possible. Custom cores are only used for accessing the sensor and for image processing algorithm based on convolution matrices [JGB04].

Peripherals are mapped into the PowerPC memory which access their registers via *iowrite() / ioread()* interface. The frames are copied to the memory via DMA.

The final FPGA design is shown is shown in the figure 4.2.

## 4.3.1.4 External Devices

Due to the limited memory resources on the FPGA it needs to be complemented with an external memory.

A non-volatile memory is also used to keep the FPGA configuration and other information such as manufacture data and the initial bootloader.

LEDs and serial ports are used for debugging purposes.

## 4.3.2 Software

# 4.3.2.1 Operating System

Although the PowerPC can run a bare metal application, it can take great advantage of the multiple services and abstractions already implemented on an OS, such as multitasking, memory management or network stack, among others.

Linux has been chosen as the OS for the camera, due to its code availability and great support from its community. Linux supports the PowerPC hard cores found on the Virtex 4 FX FPGAs and most of the Xilinx cores from its version 2.6 [Tor].

In this particular project, the only required change to the standard Linux version, has been a new module that adds support for the Image acquisition core. The module provides a custom *ioctl* and *mmap* interface for accessing the sensor. A userland library has also been developed for interfacing the module.

## 4.3.2.2 Linux Distribution

Instead of choosing an already available distribution, the limited amount of Flash memory has favored the development of a tailor made distribution based on Busybox[Ando8].

Due to the biometric nature of the project, special care has been taken to reduce the possible attack vectors to the system, this has been achieved by auditing the system and removing any unused library and service.

# 4.3.2.3 Bootloader

Before the kernel can be started, it needs to be loaded into the memory and the main memory needs to be initialized, this is done with a bootloader.

In the last years, U-boot is becoming the de-facto standard bootloader, with support for multiple boards and architectures and a lot of extra functionality such as network stack, memory test or even tools for bringing up the board.

As a contribution of this Thesis, U-boot has been ported to the embedded PowerPC available on the Virtex 4 FX and Virtex 5 FX. This change has been included in the official branch of U-boot.

# 4.3.2.4 Data Flow

Hardware and software work closely during image extraction and preprocessing. The system works following these steps:

- 1. The application on the PowerPC starts the image acquisition with an Input/Output ConTroL (IOCTL) to the custom module.

- 2. The custom module, via a register write to the acquisition core, starts exposing an image.

- 3. Once the image is exposed, the acquisition core reads the image from the sensor, via a parallel interface and process it on the fly.

- 4. The data is pushed to the main memory with a DMA transaction.

- 5. When the DMA transfer has finished, a interrupt is sent to the PowerPC.

- 6. The custom module services the interrupts and notifies the application about the new frame.

- 7. The application memory maps the new frame and process it with the CPU.

- 8. The result image data is sent through the Ethernet interface via DMA.

## 4.4 VERIFICATION AND RESULTS

# 4.4.1 Hardware Implementation

On the current implementation, it has been decided to use as many COTS modules as possible to reduce the engineering and verification time.

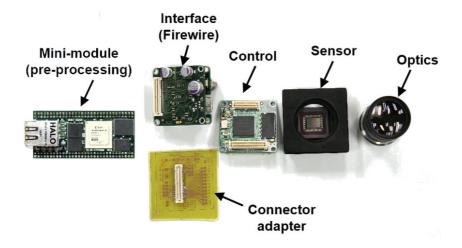

The hardware design is shown on the Figure 4.3. On that image it can be observed the different elements of the system. From left to right.

- Virtex FX12 Mini-Module, from Avnet.

- Custom Mother board, and Firewire interface from Vector (not used on the final design).

- BCI4 readout board, from Vector.

- BCI4-6600 Sensor, from Vector.

- Fixed C-MOUNT lens, from Schneider optics.

The Virtex FX12 Mini-Module by Avnet is an affordable development board, less 200\$ per unit, with a reduced form factor, 30 mm x 65.5 mm, and 76 user available I/O pins.

The custom motherboard serves as power supply for the FPGA board and the BCI<sub>4</sub> sensor as well as populating the debug connectors for the FPGA.

The whole design, including options has a price under the 1000\$. More than reasonable for a low volume, custom design.

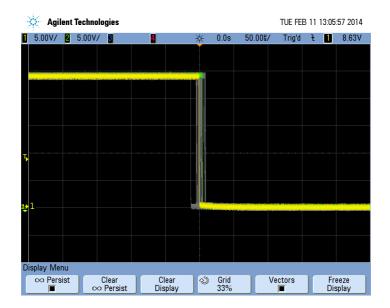

## 4.4.2 *Communication Speed*

Some experiments have been performed in order to measure the transfer speed between the platform and an external device.

For each iteration, 20 images with a size 8 MiB have been transmitted from the camera to a high-end computer. These different methodologies have been used for the data transfer:

## FPGA COMPUTER VISION SYSTEM

Figure 4.3.: Hardware used

- 1. UDP vs. TCP: Measure the overhead of the different network protocols

- 2. ZeroCopy: Measure the overhead of copying the frames to a new memory location, versus sending the frames in place.

- 3. DMA: Speed gain for using DMA on the network interface.

- 4. MTU: Implications of the datagram size on the transfer.

- 5. Link Speed: Speed gain for using a Gigabit network.

Results from these experiments are shown in Table 2.

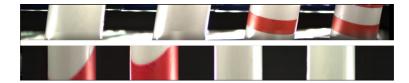

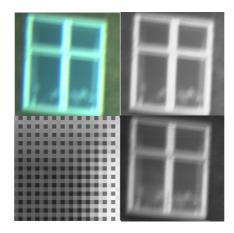

# 4.4.3 Image processing

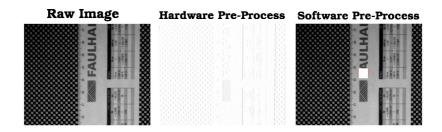

The implemented architecture can process the sensor images with hardware and software.

Hardware algorithms are developed in Hardware Description Language (HDL) using the standard Xilinx tools. On the final product, white balance and a convolution kernel were implemented. Figure 4.4 shows

| Protocol | ZeroCopy | MTU  | DMA | Gigabit | Mbps |

|----------|----------|------|-----|---------|------|

| ТСР      | Read     | 1500 | No  | No      | 32   |

| ТСР      | Read     | 1500 | Yes | No      | 40   |

| ТСР      | Mmap     | 8500 | No  | Yes     | 40   |

| ТСР      | Read     | 8500 | No  | Yes     | 40   |

| UDP      | Read     | 1500 | No  | Yes     | 56   |

| UDP      | Mmap     | 1500 | No  | Yes     | 64   |

| UDP      | Read     | 8500 | No  | Yes     | 80   |

| ТСР      | Read     | 1500 | Yes | Yes     | 88   |

| UDP      | Mmap     | 8500 | No  | Yes     | 104  |

| UDP      | Read     | 1500 | Yes | Yes     | 192  |

| ТСР      | Read     | 8500 | Yes | Yes     | 200  |

| UDP      | Read     | 8500 | Yes | Yes     | 256  |

Table 2.: Communication Speed Experiments Results

a simple vertical edge detection implemented in hardware with a convolution.

Software algorithms run on the Linux kernel, processed by the PowerPC. The only image processing library provided by the system is used to interface the custom kernel module. Figure 4.4 shows a simple pattern recognition algorithm trained for looking for the letter 'F'.

# 4.5 CONCLUSIONS

This chapter shows a custom made computer vision system implemented on an FPGA with an embedded PowerPC processor. This system is capable of acquiring and processing up to 5 frames (6.6 Megapixels) per second with hardware and software processing capabilities.

This platform has been successfully used on a commercial, state-ofthe-art product.

Although most of the parts of the system are COTS, the development of this platform required almost a whole academic year. Most of this

## FPGA COMPUTER VISION SYSTEM

Figure 4.4.: Pre-Processing Algorithms

work cannot be easily reused because the whole system has been optimized for the selected sensor.

In order to achieve real-time performance, most of the processing needs to be done on the FPGA fabric, developed using HDL languages, a tedious process with a very slow development and validation cycle.

# 5

# GPU COMPUTER VISION SYSTEM

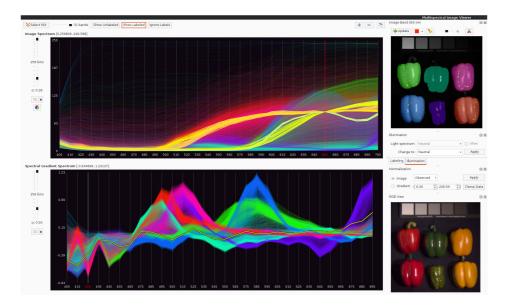

This chapter describes Computer vision System based on a standard Personal Computer (PC) architecture accelerated with a GPU.

This system has been used on Gimbaled Limb Observer for Radiance Imaging of the Atmosphere (GLORIA), a Fourier transform spectrometer that is capable of operating on various high-altitude research aircraft.

# Contents

\_

| 5.1 | Introduction 51                                      |

|-----|------------------------------------------------------|

| 5.2 | Spectrogram acquisition 52                           |

| 5.3 | Processor optimisation 53                            |

|     | 5.3.1 Motivation 54                                  |

|     | 5.3.2 Description of the Operational L0 Processor 54 |

|     | 5.3.3 Performance 56                                 |

| 5.4 | GPU acceleration 58                                  |

| 5.5 | Conclusion 60                                        |

|     |                                                      |

#### 5.1 INTRODUCTION

High altitude spectrometry is one of the best tools for measuring air quality and forecasting weather. The traditional instruments are composed by a 1-dimensional spectrometer, which provides a very limited measurement from the sky.

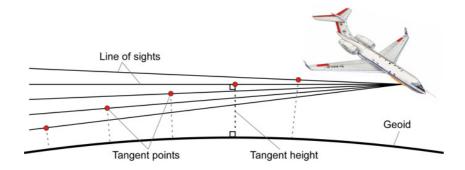

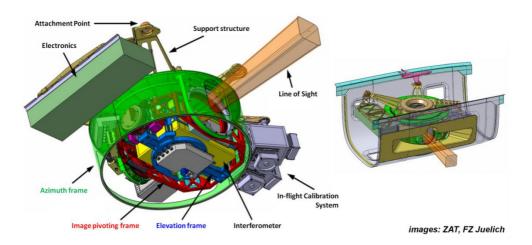

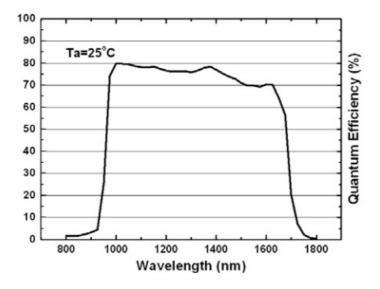

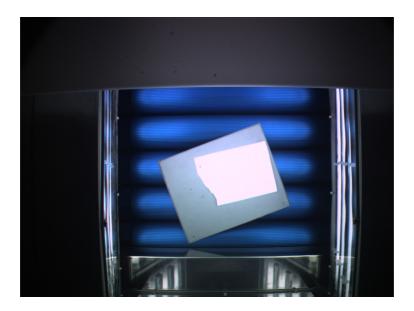

There is a combined effort from multiple German research institutes to create a high altitude bidimensional spectrometer, with a spatial near infrared sensor, denominated GLORIA (Figure 5.1).

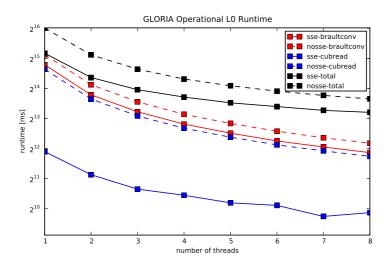

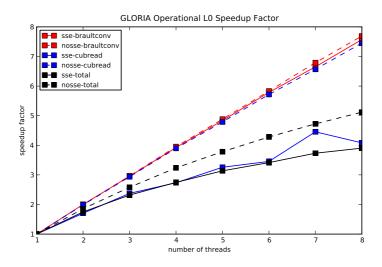

Among these institutes, Juelich Forschungszentrum is in charge of implementing the acquisition and first levels of processing of the device. The original implementation required 3 hours and 30 minutes of processing time for a interferogram that was captured in 90 seconds, which disabled the use of the instrument in weather forecast.

Thanks to the work developed on the previous chapter for U-boot, the author got in contact with Juelich Forschungszentrum. Once they were aware of his interest in Computer Vision System, a 3 month internship on their institute was arranged, where the main goal was to accelerate the first level of processing of the device.

Although the acquisition sensor could not be modified, there was complete freedom to use any platform compatible with a PC to achieve the timing goal. As a result of this work, the first level of processing was accelerated more than 200 times.

Figure 5.1.: High Altitude plane using GLORIA for acquiring interferograms

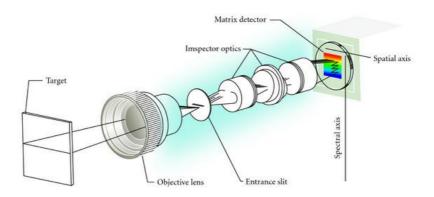

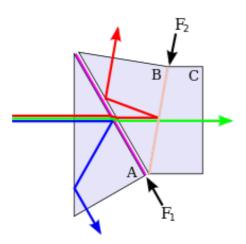

#### 5.2 SPECTROGRAM ACQUISITION

Figure 5.2 shows a detailed figure of GLORIA mounted on a high altitude aircraft.

The instrument is composed by two sensors, an infrared image sensor and a laser reference system.

The optical path difference of the interferometer is measured with a laser reference system. A diode laser signal with a wavelength of about 646 nanometers, is coupled into the interferometer, and the rising zero crossings of the laser interferogram are detected and marked with a timestamp. These timestamps are stored as laser data files. The timestamps for both the infrared and the laser signal are generated by a 80 MHz clock within the interferometer electronics. They are given in integer time ticks with one tick corresponding to 12.5 ns.

The infrared image sensor, takes images at a constant frame rate of 2665 frames per second, with 128x128 16 bits pixels.

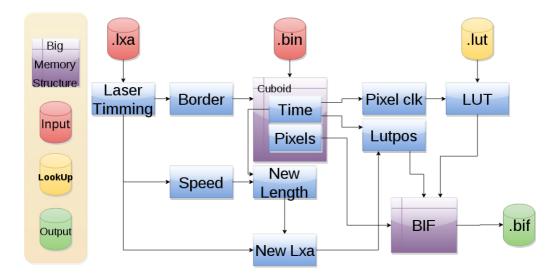

Each measurement consists of one cuboid containing the infrared signals sampled at a constant frequency (.bin file), and a laser file containing the timestamps of the rising zero crossings of the laser reference system (.lxa file).

#### 5.3 PROCESSOR OPTIMISATION

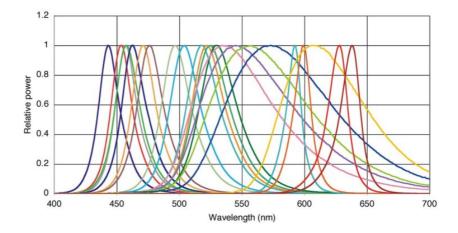

Figure 5.2.: HALO instrument